In 2006, National Semiconductor innovated the Serial Deserializer (SerDer) FPD-Link II chipset family for single-pair twisted pair differential transmission. This serialization scheme eliminates the need for data and clock paths. Skewing simplifies the task of converting a 24-bit bus on a single differential pair. The single-pair twisted pair can help reduce system layer cost by reducing the number of layers of the PCB, cable width, and connector size and pins.

This article refers to the address: http://

In traditional display system design, the graphics controller or graphics processing unit (GPU) transmits parallel RGB color bits with pixel clock and sync signal alignment. These signals use TTL levels and there are more than twenty signal lines at the remote. In the LCD display connection, the parallel bus may not exceed 20 cm to 30 cm due to problems such as too thick a cable or power supply and EMC (electromagnetic compatibility).

To solve this problem, National Semiconductor developed the Serial Deserializer (SerDes) FPD-Link (Planar Display-Link) chipset series in the mid-1990s with the leading TFT panel suppliers. The transmitter collects up to 18 bits/24 bits of RGB information (6-bit/8-bit color) and three control signals and clocks, which are then converted into three differential data pairs and one clock pair. The pair is reduced to 4 pairs and LVDS transmission is used to solve the EMC problem. It is the display interface standard for LCD TV LCD TVs.

DS90UR241/124 features

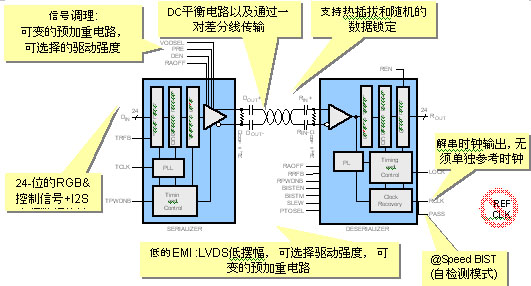

The DS90UR241/124 chipset is a 5-43MHz DC balanced 24-bit LVDS serializer/parallelizer with 24:1 and 1:24 data transfers, user-defined pre-emphasis, and AC-coupled data transfer. Embedded with Clock and Data Recovery (CDR), the supply voltage is 3.3V ± 10% for a wide range of applications. Main features: a pair of differential twisted pair transmission, simple wiring, low cost; 24-bit data serialization/deserialization (18-bit video + control signal + I2S audio); signal conditioning circuit can extend transmission to 10 meters, Meet long-distance transmission requirements; very low EMI, easy to pass the car gauge test; embedded clock in the data, so that the deserializer does not need a reference clock, reducing system cost; built-in BIST mode (convenient for factory testing / online diagnostics); Passed AEC-Q100 Level 2 (automotive certification).

Application of DS90UR241/DS90UR124 in automobile display system

The application of the car display system includes: the display of the center console, the display of the recoil headrest, the display of the car instrument, and the display of the navigation system. Others such as: head-up display system, rear view display system, camera system / sensing system / other driver assistance systems.

The general WVGA format display uses 800 × 480 WVGA resolution, 18 bits (color depth, RGB666 format), clock frequency of about 30MHz.

Figure 1: Functional block diagram of the FPD-Link II DS90UR241/124.

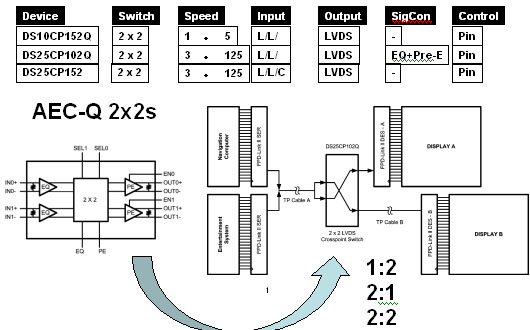

Figure 2: FPD-Link II display signal switching application (crossbar).

mirror ad,mirror advertising screen,mirror display,bathroom smart mirror,mirror advertisement,bathroom mirror advertising,interactive bathroom mirror,digital mirror for bathroom,bathroom magic mirror,bathroom digital mirror

Guangdong Elieken Electronic Technology Co.,Ltd. , https://www.elieken.com