This design guide discusses how to design an RS-485 interface circuit. The necessity of balancing the transmission line standard is discussed in the paper, and a process control design example is given. The line also discusses the line load, signal attenuation, fail-safe, and galvanic isolation.

1. Why Balance Transmission Line Standards The focus of this paper is on the industry's most widely used balanced transmission line standard: ANSI/TIA/EIA-485-A (hereafter referred to as 485). After reviewing some of the key aspects of the 485 standard, a factory automation example is used to introduce how to implement a differential transmission structure in an actual project. In long-distance, high-noise environments, data transfer between computer components and peripherals is often difficult, and if possible, use single-ended drivers and receivers. For systems that require long-distance communication, a balanced digital voltage interface is recommended. The 485 is a balanced (differential) digital transmission line interface developed to improve the limitations of TIA/EIA-232 (hereafter referred to as 232). The 485 has the following features: "· High communication rate – up to 50M bits/s · Long communication distance – up to 1200 meters (Note: 100Kbps) · Differential transmission – Small noise radiation · Multiple drivers and receivers in practice In applications, 485 drivers, receivers, or transceivers can be used if low-cost, reliable data communication is required between two or more computers. A typical example is the use of 485 transmission between a sales terminal and a central computer. Information. The use of twisted pair transmission balanced signals has low noise coupling, plus 485 has a wide common-mode voltage range, so 485 allows communication at rates up to 50M bit/s, or thousands of kilometers at low speeds. Distance. Due to the wide range of 485 applications, more and more standards committees use the 485 standard as the physical layer specification for their communication standards, including ANSI SCSI (Small Computer System Interface), Profibus standard, DIN measurement bus, and China's multi-function power. Table communication protocol standard DL/T645.

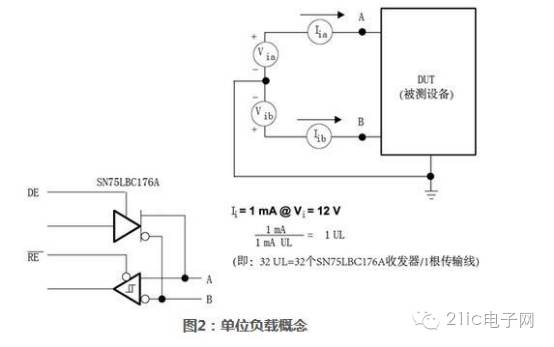

2. System Design Considerations 2.1 Line Load In the 485 standard, the line load should take into account the load on the line termination and transmission line. Whether the transmission line terminal is matched depends on the system design, and is also affected by the length of the transmission line and the signal rate (in general, the low speed and short distance may not be matched by the terminal). 2.1.1 Transmission line termination matching The transmission line can be divided into two models: distributed parameter model [1] and lumped parameter model [2]. Which model the test transmission line belongs to depends on the transition (rise/fall) time tt of the signal and the propagation time tpd of the driver output to the end of the cable. If 2tpd ≥ tt/5, the transmission line must be processed according to the distributed parameter model, and the transmission line terminal matching must be handled; in other cases, the transmission line is regarded as a node parameter model, and the transmission line terminal matching is not necessary. Note 1: Distributed Parameter Model - The voltage and current in the circuit are a function of time and are related to the geometry and spatial position of the device. Note 2: Lumped Parameter Model - The voltage between any two endpoints in the circuit and the current flowing into the endpoint of either device are fully determined, regardless of the geometry and spatial position of the device. 2.1.2 Unit load concept The maximum number of drivers and receivers attached to the same 485 communication bus depends on their load characteristics. The load on the driver and receiver is measured against the unit load. The 485 standard specifies that up to 32 unit loads can be attached to a single transmission bus. The unit load is defined as the allowable current through a steady-state load of 1mA in a 12V common-mode voltage environment, or a steady-state load of 0.8mA in a -7V common-mode voltage environment. The unit load may consist of drivers, receivers, and fail-safe resistors, but does not include AC termination matching resistors. Figure 2 shows an example of the unit load calculation for the SN75LBC176A transceiver. Because the device integrates the driver and receiver together to form the transceiver (that is, the driver output and receiver inputs are connected to the same bus), it is difficult to obtain the driver leakage current and the receiver input current separately. For ease of calculation, the receiver input impedance is considered to be 12 kΩ and the transceiver is mA current. This can represent a unit load, and 32 such loads are allowed on the transmission bus.

As long as the receiver's input impedance is greater than 12kΩ, more than 32 such transceivers can be used on a single transmission bus.

2.2 Signal Attenuation and Distortion A useful common sense is to allow signal attenuation of -6 dB at maximum signal rate (unit: Hz) communication. In general, the cable supplier will provide a signal attenuation chart. The curve shown in Figure 3 shows the relationship between 24-AWG cable attenuation and frequency.

The easiest way to determine the extent to which random noise, jitter, distortion, etc. affect the signal is to use an eye diagram. Figure 4 shows the signal distortion at the receiving end at different signal rates using a 20AWG twisted pair cable at 500 meters. As the signal rate increases further, the effects of jitter become more pronounced. At 1 Mbit/s, the jitter is about 5%, and at 3.5 Mbit/s, the signal is completely overwhelmed and the transmission quality is severely degraded. In practical systems, the maximum allowable jitter is typically less than 5%.

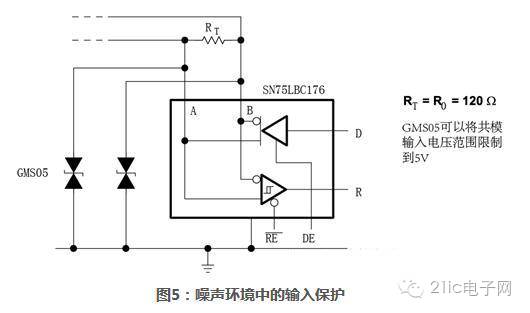

2.3 Fault protection and failure protection 2.3.1 Fault protection As with any other system design, fault response measures must be habitually considered, whether they are naturally occurring or environmentally induced. For factory control systems, extreme noise voltages are typically required to be protected. The differential transmission mechanism provided by 485, especially the wide common-mode voltage range, makes 485 have some immunity to noise. However, in the face of complex and harsh environments, its immunity may be insufficient. There are several ways to provide protection. The most effective method is galvanic isolation, which is discussed later. Galvanic isolation provides better system level protection, but at a higher price. A more popular and less expensive solution is to use diode protection. Using a diode approach instead of galvanic isolation is a compromise that provides protection at a lower level. An example of an external diode and an internal integrated transient protection diode is shown below: The 485 transceiver SN75LBC176 shown in Figure 5 is externally connected to a diode to prevent transient glitch.

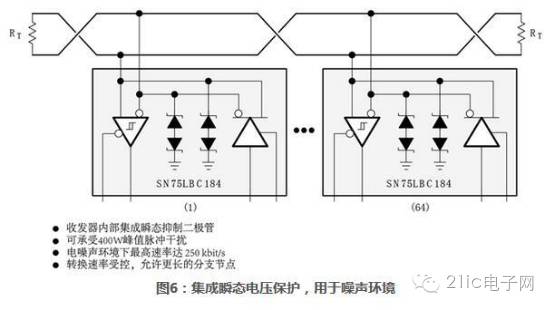

Figure 6 shows the 485 transceiver SN75LBC184 with an internal integrated TVS diode for applications where full 485 functionality is desired and PCB space is limited. The SN75LBC184 integrates a protection diode internally to directly replace the SN75LBC176 for high energy electrical noise environments.

2.3.2 Failure Protection Many 485 applications also require fail-safe protection. Failure protection is useful for the application layer and requires careful consideration and full understanding. In an interface system where any of the multiple drivers/receivers share the same bus, the drive is inactive for most of the time, and this state is referred to as the bus idle state. When the drive is in an idle state, the driver outputs a high-impedance state. When the bus is idle, the voltage along the line is floating (that is, it is not high or low). This can cause the receiver to be erroneously triggered high or low (depending on ambient noise and the last level polarity before the line is floating). Obviously, this situation is unpopular. An associated circuit is required in front of the receiver to change this indeterminate state to a known, pre-agreed level, which is referred to as fail-safe. In addition, fail-safe protection against data errors due to short circuits. There are many ways to implement fail-safe protection, including adding hardware circuitry and using software protocols. Although the software protocol is more complicated to implement, it is the preferred method. However, because most system designers and hardware designers prefer to use hardware to implement fail-safe protection, adding hardware circuits to implement fail-safe protection is more often used. The fail-safe circuit must provide a clear input voltage to the receiver, whether short-circuited or open-circuited. If the communication line is in a very harsh environment, line termination matching is also necessary. Many manufacturers have begun to integrate some fail-safe circuits (such as open-circuit fail-safe) into the chip. Usually these extra circuits only add a large value pull-up resistor at the receiver's non-inverting input and a large value pull-down resistor at the receiver's inverting terminal. These two resistors are typically around 100KΩ. These resistors and termination matching resistors form a potential driver that can only provide a differential voltage of a few mV. Therefore, this voltage (receiver threshold voltage) is not sufficient to switch the receiver state. Using such an internal pull-up resistor allows the bus to not perform termination matching, but significantly reduces the maximum signal rate and reliability. Figure 7 shows some 485 interface universal external fail-safe circuits. Each circuit tries to maintain the receiver input voltage not less than the minimum threshold and maintain one under one or more fault conditions (open, idle, short). Known logic state. In these circuits, R2 represents the transmission line impedance matching resistor and becomes part of the voltage driver: producing a steady state bias voltage. It is assumed here that each receiver represents 1 unit load. The table in the right half of Figure 7 lists some typical resistor and capacitor values, the type of failsafe provided, the number of unit loads used, and signal distortion. In the next section, the resistance values ​​in the short-circuit-failed circuit are calculated to illustrate how to modify these resistor values ​​to suit a particular design.

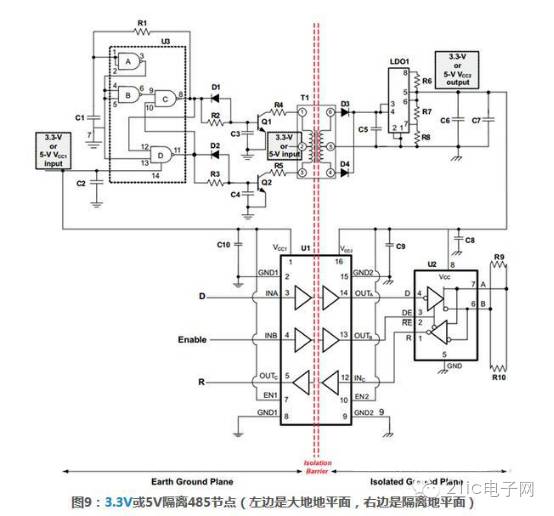

2.4 Galvanic isolation Computers and industrial serial interfaces are often in a noisy environment and may affect the integrity of data transmission. For any interface circuit, the tested method to improve noise performance is galvanic isolation. In data communication systems, isolation means that there is no direct current flow between multiple drivers and receivers. An isolation transformer provides power to the system, and optocouplers or digital isolation devices provide data isolation. Galvanic isolation removes ground loops and rejects noise voltages. Therefore, using this technique can suppress common mode noise and reduce other radiated noise. As an example, Figure 9 shows a node of the process control system that connects the data logger to the host computer via a 485 link. When an adjacent motor is started, the ground potential of the data logger and the computer will be instantaneously different, which usually causes a large current. If the data communication does not use an isolation scheme, the data may be lost and, in the worst case, the computer may be compromised. 2.4.1 Circuit Description The schematic shown in Figure 9 is a node of a distributed monitoring, control, and management system that is typically used for process control. Data is transmitted over a pair of twisted pairs, and the ground wire uses a shield. Such applications often require low power consumption because many remote substations use batteries or require a backup battery (after a power failure, the device needs to be able to use the backup battery for a certain amount of time). In addition, with a low power count, a small isolation transformer can be used. As shown in Figure 9, the transceiver uses the SN65HVD10. Of course, any TI 3.3V or 5V RS485 transceiver, 3.3-V TIA/EIA-644 LVDS or 3.3-V TIA/EIA-899 M-LVDS transceiver can use this. Circuit. 2.4.2 Operation Principle The example shown in Figure 9 can be used for 3.3V or 5V. The power supply is isolated by transformer and the data signal is isolated by digital isolators. Because 485 transceivers require isolated power, the tunable LDO regulator must be isolated. This function can be implemented using a NAND gate oscillator circuit to drive an isolation transformer. The output voltage of the transformer is adjusted and filtered for use by a low dropout linear regulator. In high EMI environments, this approach is often used to prevent noise from other remote power subsystems from coupling to the mains. The TPS7101 is used to power other electronic components and provides up to 500mA. By adjusting the bias resistor R7, the TPS7101 can output 3.3V or 5V. See the BOM list for specific resistance values.

The data signal isolation is completed by a three-channel digital isolator ISO7231M. The device provides 2.5KV (rms) voltage isolation and 50KV/us instantaneous discharge protection at 150Mbps signal rate.

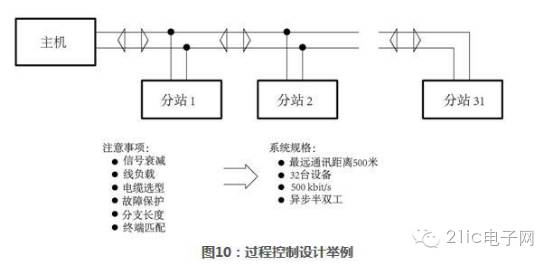

3. Process Control Design Example In order to obtain more knowledge of 485 system design, a better method is to look at specific examples. Consider a system in which the system has a main controller and several sub-station factory automation systems, each of which can send and receive data. The system characteristics are shown below, and the general specifications are shown in Figure 10. · The farthest substation is 500m from the main controller · 31 substations (plus a total of 32 devices) · Signal transmission rate is 500 kbit/s

· Half-duplex communication

Ningbo Autrends International Trade Co.,Ltd. , https://www.supervapebar.com