Pick  Important : This article introduces the performance characteristics and design considerations of the ADS5500 , and briefly describes its application in video signal processing.

Overview

In recent years, with the rapid development of digital signal processing technology and the continuous emergence of new theories and algorithms, coupled with the overall improvement of the performance of digital signal processing devices, the actual system has increasingly higher requirements for analog-to-digital converters. Therefore, in practical applications, it is generally required that the analog-to-digital converter must have a high sampling rate and accuracy, a large dynamic range, an extremely wide frequency response range, and a flexible digital interface at the same time.

ADS5500 is a high-performance analog-to-digital converter with 14 -bit resolution and 125MSPS sampling rate developed by TI . The chip is a 64- pin TQFP PowerPAD package. In order to achieve higher system integration, it also includes a wide bandwidth linear sample / hold and a complete conversion solution for the internal reference voltage source. When ADS5500 100MHz signal to noise ratio (SNR) 70dB, and a distortion-free dynamic range (SFDR) of 82dB, the differential input voltage is 2.2Vpp, the working voltage of 3.3V (unipolar), and the power consumption of only 750mW. The internal reference voltage source simplifies the system design, and the parallel CMOS compatible data output interface ensures the seamless connection with the ordinary logic circuit, which facilitates the connection with the digital signal processor. Its internal structure is shown in Figure 1 .

Figure 1Â The internal structure block diagram of ADS5500

Picture 2Â ADS5500 working signal timing

Figure 3Â Analog input section

Design considerations

ADS5500 is a low power, 14-bit sampling rate 125MSPS pipelined analog to digital converter, only a single polarity power supply of 3.3V can work properly. The data conversion process starts on the rising edge of the clock signal waveform. Once the analog signal is captured by the sample / hold part of the converter, the sampling process of the input signal is sequentially divided into a series of pipeline operations to make the clock signal rise and fall Data conversion can be carried out at all edges. A delay of 16 clock cycles is required from inputting an analog signal to outputting 14 -bit data . Figure 2 shows the corresponding timing of ADS5500 input and output signals and clock waveforms.

Input configuration

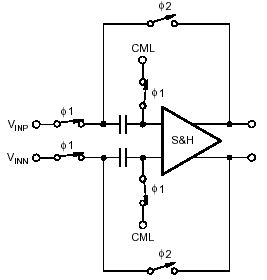

The analog input part of ADS5500 is mainly composed of a differential track / hold amplifier and switched capacitor ( Figure 3) .

Differential input technology ensures high performance under high sampling rate conditions, while also bringing a very high usable input bandwidth, which is particularly important for some intermediate frequency sampling or under-sampling applications.

For the input configuration of low-frequency input signals, a differential input / output amplifier ( such as OPA695) can be used to simplify the front-end drive circuit. The advantage of this configuration is that it has greater flexibility. The amplifier can be used to complete the polarity conversion ( unipolar to differential ) of the analog input signal , signal amplification, and ADC front-end pre-filtering.

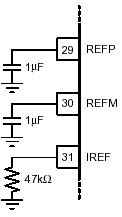

Reference source circuit

The internal reference voltage source of ADS5500 simplifies the circuit layout of the circuit board. For this, other additional circuits are not required on the board. But from the perspective of optimizing performance considerations, can be connected to a respective capacitor in 1mF REFP and REFM pins and grounded. Further, in order to better set the operating current of the chip, is also connected to a 47 Ω resistor in the IREF pin, and is connected to pin AGND (FIG. 4).

Picture 4Â REFP , REFM and IREF pins optimize system performance

Picture 5Â Clock input signal pin connection circuit

Figure 6 ADS5500 builds a real-time image processing system

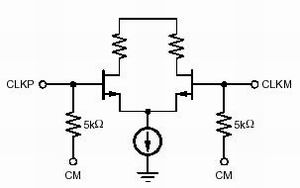

Clock input signal

The clock input signal of the chip can be unipolar or differential signal. In normal mode, the voltage amplitude of the clock input signal is set to 1.5V , and the CLKP pin and CLKM pin are connected to the CM pin through a 5k Ω resistor ( Figure 5 ) .

From a practical point of view, selecting a low-jitter clock source and performing corresponding band-pass filtering on it can greatly improve the performance of the high-frequency sampling system. The ADC core inside the chip can perform data conversion on the rising and falling edges of the clock signal waveform, which further improves the working efficiency of the chip. When there is no clock source or the clock frequency is lower than 10MSPS , the chip will automatically switch to sleep mode.

Output options

Chip generates an output signal data of 14 bits (D13-D0), 1 data ready signal (CLKOUT pin) and an indication bit data overflow (OVR pin, the output data when the amplitude exceeds the maximum value, the bit is set For 1) .

The data format of the output signal and the polarity of the clock output signal can be set by changing the level of the DFS pin. The data format of the output signal has two forms: direct binary code and two's complement, and the clock polarity shows that the output data is valid on the rising or falling edge of the clock waveform. There are four selection ranges for the DFS pin level, so there are four corresponding relationships. Table 1 shows the correspondence between these four modes.

Application examples

Figure 6 is a real-time image processing system. The CCD sensor sends the original image ( analog signal ) to the ADS5500 for high-frequency sampling to obtain a high-precision digital image signal, which is then sent to the image processing unit through a high-speed synchronous FIFO , and the digital signal processor Finish the image processing and compression, and display the processed data on the liquid crystal display or CRT display.

Concluding remarks

The ADS5500 interface is simple, easy to use, flexible, 14 -bit sampling accuracy, and at the same time has a very high conversion speed. In most applications that require high-speed data acquisition and high-precision measurement, this chip has strong practicability.

2 In 1 Laptop

Do you know the difference of Yoga Laptop and 2 in 1 laptop? No. 1 is yoga notebook with 360 flip rotating absolutely; No.2 is laptop yoga slim is just like normal Education Laptop-connecting screen with keyboard, but 2 in 1 laptop tablet with pen is separately, you can use the monitor part as a window tablet. In one word, every intel yoga laptop have all the features and function of tablet 2 in 1 laptop except separated screen and keyboard. From the cost, windows yoga laptop is much higher than 2 in 1 type., cause usually former with more complicated craft and quality.

What other products you mainly produce? It`s education laptop, Gaming Laptop, engineering laptop, Android Tablet, Mini PC and All In One PC. You can see more than 5 different designs on each series, believe always have right one meet your special application or your clients demands. Therefore, what you need to do is just to get all the requirement details from your clients, then share the complete information with us, then we can provide the most suitable situation.

Of course, you can also call or email or send inquiry of what you need, thus can get value information much quickly.

2 In 1 Laptop,2 In 1 Laptop Sale,2 In 1 Laptop Tablet With Pen,Tablet 2 In 1 Laptop,2 In 1 Laptop Deals

Henan Shuyi Electronics Co., Ltd. , https://www.shuyicustomtablet.com