When I graduated, I was young and frivolous, thinking that I could be alone, and what I learned on the temple was enough to meet the needs of the industry. However, in the course of my work, I got to know a lot of cattle people, and I learned a lot from them. I summed up the knowledge structure that an IC design engineer needs, and I want to share it with you.

Skill listAs a truly qualified digital IC design engineer, you will always need to continue to learn more advanced knowledge and technology. Therefore, the skills listed here will never be complete. I try to update this list once a year. If you feel that this list is not comprehensive, you can leave a message under this article, I will try to complete it.

Language class: Verilog-2001/ VHDL, SystemVerilog/ SystemC, Makefile/ Perl/ Python/ Shell, Tcl

Tools: NCVerilog / VCS / ModelSim, SimVision / DVE / Verdi, Vim / Emacs, SVN / CVS / Git, Microsoft Office

Platform class: Windows, Linux, OS X

Other plus points: MATLAB, ISE/Synplify/Vivado/Quartus, LEC/Formality, VMM/UVM, ESL, ZeBu Server, JIRA/Confluence, C/ Assembly Language, Computer Architecture/ ARM Architecture/ MIPS Architecture

Why & What to doA) Verilog-2001/ VHDL

The reason why Verilog-2001 is emphasized here instead of Verilog-1995 is because many new features are specified in Verilog-2001, so it can produce a better code style.

I have given a detailed example of the new interface syntax in the article What is a good Verilog code style. This new interface method is much simpler to modify, and it is more convenient to use when instantiating the module. Unlike the old interface syntax, because an interface needs to be described in three times, the endless end increases the number of lines of code and is difficult to read and change. This advantage of Verilog-2001 is especially prominent when the number of interfaces of a module exceeds the display range of one screen.

The biggest problem in learning Verilog is that many domestic writings are very bad. Many of the examples in the book exist to illustrate the grammatical features. There is no practical value, and even a lot of code is wrong. It is not that he has a grammatical error, but that he is incomparable and cannot be achieved by digital circuits.

So, for learning Verilog, my suggestion is to just find a book similar to the grammar manual and rush through the basic grammar to figure out the module definition, interface definition, module instantiation, register definition, line definition, and always blocks. After writing these basics, I started to download the complete open source project code that has been verified by FPGA on the OpenCores website. First, you can understand the code written by others, and then try to imitate yourself. If you don't understand the problem, you can search for the answer online.

The biggest difference between the Verilog language and the software language is that because it is used to describe circuits, its writing is very fixed, because the circuit changes are very limited. When learning Verilog, many times we are not learning the language itself, but learning its corresponding circuit characteristics and how to describe this circuit.

If you don't have a circuit in your heart, then you can't write Verilog. Starting from the basics, it is very important to accumulate a small circuit description method like a timer. Verilog encourages innovation in circuits rather than innovating in describing methods. Therefore, even the world's most popular Verilog master, the Verilog code syntax he wrote is very common, and his idea is how to combine these basic small circuits.

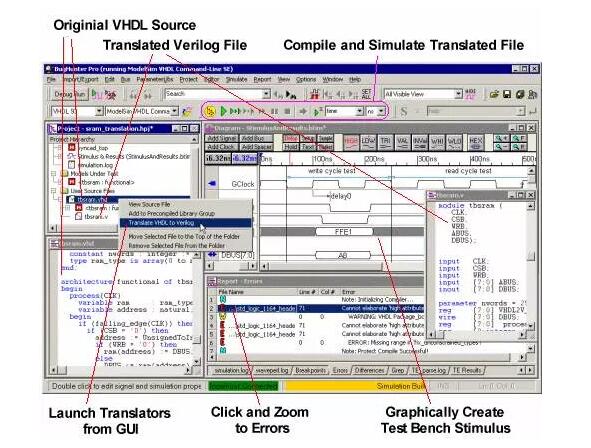

Although I don't know much about VHDL, in many countries in Europe, VHDL is still the mainstream RTL design language. The rigor of the VHDL language is better than that of Verilog. Unlike Verilog, there are a large number of statements that conform to the syntax but can never be synthesized. It is easy to mislead the newcomers (the code passed by the simulation is reported in the FPGA synthesis, or the FPGA implementation results are inconsistent with the simulation) . While VHDL and Verilog can be transformed into each other, there are still many problems in the conversion process, and it is impossible to fully automate. I have written a topic on this point to explore how to convert VHDL to Verilog. Interested students can go and see.

B) SystemVerilog/ SystemC

Both languages ​​exist for verification. As an IC design engineer, verification knowledge is not required, but mastering basic verification methodologies can help improve your debug efficiency and results. I have introduced a verification method that I have summarized in detail in the article How to quickly build a module verification platform. This method is based on the SystemVerilog syntax. Because SystemVerilog is fully compatible with Verilog, just as C++ is compatible with C, it is not difficult to learn SystemVerilog (or SV).

SystemVerilog is an object-oriented language. Its design is intended to build a verification platform. The mainstream VMM/UVM methods are also based on SystemVerilog, so they are determined to become IC verification engineers, SystemVerilog's in-depth learning and popular methodology. Learning is essential.

For those who only want to do IC design, SystemVerilog is also worth learning. Not to mention the debug method mentioned above for improving verification efficiency, SystemVerilog is useful even for design purposes. In many developed countries in Europe and America, many of the world's top IC design companies have begun to use SystemVerilog for RTL design. Because SystemVerilog adds a lot of new syntax like always_ff, always_comb, etc. to explicitly indicate the intention of the integrated circuit, the code is more readable, and the ambiguity is reduced in the synthesis process, ensuring the comprehensive result and design intent as much as possible. Consistency. From another perspective, the addition of assertTIon also greatly improves the debugging efficiency of the code, which is very helpful to locate the initial point of error in the process of large-scale data interaction. Students who have not mastered can spend more time researching it. .

C) Makefile/ Perl/ Python/ Shell

The above four are common scripting languages ​​used by IC design engineers. It seems that they are not related to the professional capabilities of IC design. However, because the professional tools in this industry are very expensive, the project requirements are very different, so master one. A handy scripting language will help you greatly improve your productivity. If you haven't tried to write your own scripting language, then ask yourself, have you ever been late for the night to complete a batch of simulation use cases? Have you ever been blinded by tens of thousands of data? Have you ever been crazy about modifying the bit width of a global signal? What if I want to convert a hex type data file to a special format that is required by the memory model? That's right, if you have mastered the scripting language, these strange requirements are not a thing, and repeated and meticulous manual labor is given to the computer to complete. The slogan I have always believed in is: But if you do it once, there is no need to repeat it a second time.

If you have used a platform or script developed by other engineers at work, it is likely to be written in these 4 languages. If the way to execute the script is make run, then it is likely that you are using a Makefile script; if the execution mode is source run, then this should be a script written in the Shell language; if it is otherwise, then you have to look at this specific How was the first line of the script written? The Makefile and Shell languages ​​are easier to use than Perl/Python, and are easier to write, and are better suited to meet some very simple batch task requirements. Perl's strength lies in its powerful text processing capabilities and omnipotent CPAN library, ready to meet your various willful needs. The advantage of Python is better maintainability.

Regarding the importance of scripting languages, you can check out the discussion here: What are the uses of scripting languages ​​such as Perl in IC design? .

D) Tcl

Strictly speaking, Tcl is a very simple and simple language, and its difficulty in learning is that it is not enough to master its grammar. This situation is a bit like javascript. If you use js to develop web pages, then you must have a deep understanding of DOM and HTML. If you use js to develop games, you must have a deep understanding of the various aspects of the Unity3D engine; if you use js to develop Web App, then you must use the various libraries of node.js and the common server side framework.

Language is always just a tool, and this sentence is perfect for Tcl. In the field of IC design, Tcl is a very common language. It can be used to describe timing and pin constraint files, UPF information, and can also be used to build a simple work platform. It is not only the scripting language supported by many EDA tools in the IC field, but also the file format of these tool configurations and outputs. Therefore, being able to read Tcl and master the basic grammar of Tcl language can help you better use EDA tools. It is really Tcl, I have it!

However, Cheng Xiao also lost Xiao He, as mentioned at the beginning of the previous article, just mastering the grammar of Tcl is far from all. Different EDA tools provide different command and parameter support for Tcl scripts. Whenever you need to write Tcl scripts for a new tool, you must read the official user manual to understand the tool support. The Tcl command structure ensures that the scripts that are written can be executed correctly.

E) NCVerilog / VCS / ModelSim / iVerilog

The above three are comparatively mainstream simulation tools. NCVerilog and VCS only support the Linux platform, while ModelSim seems to support both the Linux platform and the Windows platform. But no matter which one, I hope everyone can realize two things:

First, the emulator and the waveform viewer are two different things. This entry introduces only the emulator. The working principle of the emulator is different from that of the waveform viewer. At the same time, due to the IEEE standard for the standard waveform file *.vcd format. Any emulator can be combined with an arbitrary waveform viewer.

Second, the emulator usually has no graphical interface. In order to use the emulator better, you should familiarize yourself with the user manual of the common emulator and understand the command line parameters of some common requirements. At least, you need to know the following: How to Specify the compiled file type, how to specify the compiled file list, how to specify the index directory, how to specify the simulation precision, how to specify temporary macro variables, how to specify the strict level of syntax checking, how to mix and compile projects written in multiple languages, how to Call the pli interface of different waveform generation tools, how to cooperate with SDF anti-standard for post-imitation and so on.

The functions of different emulators are actually similar, but is it possible to play all over the world with only one emulator? of course not. In actual engineering, we often use third-party IP cores. Sometimes, for the sake of confidentiality, third-party IP cores will be provided in the form of encrypted binary files. What is the length of encrypted binary files?

They are generally named in the "*.vp" format. The beginning of the file is the standard Verilog syntax, but it becomes garbled after a line of comments. Usually the line of comments before the garbled specifies the type of emulator supported by the encrypted binary. So you see, if you are a serious VCS user, and one day the project manager suddenly gives you an encrypted file that only supports NCVerilog, you will have thousands of grassy horses whizzing through.

F) SimVision/ DVE/ Verdi/ ModelSim/ gtkWave

Corresponding to the above simulator, the above three are also the mainstream waveform viewing tools in the industry. All waveform viewers must support the standard waveform file *.vcd format, but due to the poor storage performance of *.vcd format and too much redundant information, each waveform viewing tool has launched its own uniquely supported waveform. File formats such as *.vpd for DVE, *.fsdb for Verdi, *.wlf for ModelSim, *.shm for SimVision, etc. Usually the file format that is supported by the Wave Viewer has a high compression ratio.

For example, the *.vcd format waveform of about 1G is usually only about 40MB after being converted to *.vpd format, and it is usually smaller after conversion to *.fsdb, so the standard waveform file *.vcd is converted to other compression format. More conducive to data backup.

If you do not want to produce *.vcd during the simulation, but directly generate other waveform viewer-specific formats with higher compression ratio, you need to call the pli interface provided by the corresponding tool, and cooperate with the system function call in the test platform code (such as $fsdbDumpOn, etc.) to complete.

G) Vim/ Emacs

I often see some Verilog newcomers asking such a ridiculous question: "What kind of software do you use for general Verilog programming?

First, Verilog is a circuit description language that may be closer to the blood of the circuit diagram in nature, at least not to describe the description process as "programming."

Secondly, there is no special software for writing Verilog. Most engineers in the industry use Verilog code files such as Vim or Emacs to write Verilog code. If you want to use Notepad or Texteditor, you can write it. But if you have an in-depth understanding of Vim or Emacs, you will naturally understand why so many people choose them - to improve efficiency.

1. Have you ever been staggered by the boss after the code is written? You have not put all the reg and wire definitions in the same position of the file (such as line 38)? If you use the Vim editor, you only need to use: g%^\s*reg\s*%m 38 plus: g%^\s*wire\s*%m 38.

2. Have you ever been asked to delete all the comments in a file? Just need: %s%//.*$%%g.

3. Have you ever needed to instantiate a module 256 times, and then you can't use the for loop directly because of a small difference in each instantiation? It doesn't matter, with the qq recording function, you only need to operate once, then use 256@q to automatically repeat your actions 256 times.

4. Have you ever encountered a broken keyboard, the “a†key often fails or even does not respond? It doesn't matter, use: inoremap 'a' to remap the 'key' to the a key.

Similar examples are countless, see Vim Practical Tips for Verilog for more information.

So, the biggest benefit of using Vim or Emacs is that you will feel your brain is busier than your hands, because it takes only a very short time from the time you want to know that the code is written. You can put all your energy into the content of the code, not the process of entering the machine into the code, as if you were using a typewriter instead of a brush. As long as you can programmatically describe things clearly, Vim can be done quickly instead of you, provided that you have to learn a lot of Vim commands and regular expressions to ensure that your representations are properly understood by the editor.

G) SVN/ CVS/ Git

All three are currently the more mainstream "version management" tools. What is version management?

In short, it is a tool for recording and querying file version changes, usually deployed on a public server to ensure data is secure and recoverable. At the beginning of the project, you first need to create the root directory of the version management, and then the engineers will add their own design files to the subdirectories of the version management for the first time.

During the execution of the project, whenever someone changes a file, the version management tool needs to upload the code and comment the changes. The version management tool will automatically check whether the changes conflict with the latest version on the server (the meaning of the conflict is that In the process of the engineer changing the file, someone else also changed the same line of code of the file and uploaded a new version. If there is no conflict, the newly uploaded changes will be automatically merged into the latest version. On the contrary, the conflicting parts are compared and displayed, so that the engineer can manually judge how the content of the conflicting line should be merged, and the conflict can be re-uploaded after the conflict is resolved.

H) ISE/ Synplify/ Vivado/ Quartus

Both ISE and Vivado are FPGA tools from Xilinx. ISE is old and officially stopped updating. The latest version is 14.7, and Vivado continues to be updated as a new generation of FPGA tools. Quartus is an FPGA tool from Altera, and its features are similar to those of ISE/Vivado. I don't have much contact with FPGA tools on weekdays, but from a limited contact experience, Quartus is more suitable for learning than ISE/Vivado. The threshold for entry is lower and the interface is easier to learn (but don't Use the waveform simulation tool that comes with the Quartus version 6.2 or later, which is garbage).

I) Windows / Linux / OS X

I believe that most people's personal computers use the above systems or other systems similar to the above systems. The above three systems, for professional digital IC front-end designers, the ease of work (note that it is the convenience of professionals, not the steepness of the learning curve, here is the premise that they have reached the proficiency The help of work efficiency) from convenience to difficulty are: Linux "Windows" OS X.

Under Windows, you may need Cygwin (simulated Linux shell with most GNU tools), Modelsim, Debussy (renamed Verdi does not have a corresponding version of Windows), Quartus, ISE, etc. Under Linux, you may need tools such as Bash/Csh/Tcsh, Modelsim, Quartus, ISE, VCS, Simvision, DVE, NCVerilog, Formality, LEC, Synplify, etc. In OS X (I am unfortunately located under the platform), the tools you can use are only Bash/Csh/Zsh, iVerilog, gtkWave.

It is not difficult to see from the above that in terms of the diversity of tools, Linux has exploded to other platforms, which is one of the main reasons why most IC development companies' servers are deployed under Linux. For personal computers, most students will choose to use virtual machines to take into account the choice of tools on different platforms. Personally, it is recommended that you understand the Linux platform and its tools, and also understand the solutions of other platforms.

PS article by Kellen Wang, with partial deletion

Huaqiang Jufeng owns three main businesses of electronic enthusiasts (million electronic engineer community platform:), Huaqiang PCB (multilayer circuit board manufacturing experts:), Huaqiang core city (electronic components and SMT online mall:), with Internet information Technology to improve the traditional manufacturing industry, open up the upstream and downstream of the electronic industry chain, form a one-stop service platform to serve the entire electronics industry chain, reduce costs, improve quality and accelerate the process for customers.

Dp Fiber,Fiber Dp,Fibre Dp,Dp Over Fiber

Dongguan Tuojun Electronic Technology Co., Ltd , https://www.fibercablessupplier.com