Recently, I am doing video output on Spartan6. The output interface is HDMI interface, and the required format is 720P.

The system clock has

1. 750M (IO output clock of TMDS output, must be connected to bufpll)

2. 75M (720P pixel clock)

3. 150M

4. 100M (system clock)

5. 24M (clock required for peripherals)

The tool is ISE12.2

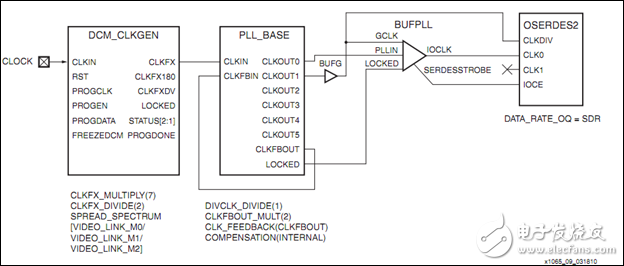

Then use the Clock_wizard that comes with ISE to generate the required clock. The 750M is dedicated to the IO output clock of TMDS. The main ports are defined as follows:

--Clock_gen is automatically generated by Clock_wizard.

Clock_gen_inst : clock_gen

Port map(

CLK_IN1 => sys_clk_in,

RESET => sys_rst,

LOCKED => LOCKED,

CLK_OUT1 => pix_clkx10_pll, --750M, need bufpll as buffer

CLK_OUT2 => pix_clk_pll, --75M

CLK_OUT3 => pix_clkx2_pll, --150M

CLK_OUT4 => sys_clk, --93.75M

CLK_OUT5 => external_clk_buf );

And pix_clkx10_pll must add bufpll

BUFPLL #(

.DIVIDE(5)

)

Tx_bufpll_inst(

.IOCLK(tx_clkx10),

.LOCKED(LOCKED),

.LOCK(LOCK),

.PLLIN(pix_clkx10),

.GCLK(pix_clkx2),

.SERDESSTROBE(tx_serdesstrobe));

According to the above clock definition, such an error occurs during mapping:

ROR: Place - ConstraintResolved NO placeable site for U2/tx_bufpll_inst

ERROR: Place - SIO has over-constrained componet U2/tx_bufpll_inst to have to placeable sites. Constraints come from

Driver constraints AND load IO constraints

Phase 4.2 IniTIal Placement for Architecture Specific Features (Checksum:fc8413ca) REAL TIme: 38 secs

Total REAL TIme to Placer compleTIon: 38 secs

Total CPU time to Placer completion: 38 secs

ERROR:Pack:1654 - The timing-driven placement phase encountered an error.

Mapping completed.

See MAP report file "hdmi_top_map.mrp" for details.

Problem encountered during the packing phase.

Trying many times or reporting an error by adding a PLL or deleting one of the clocks. I found it on the Internet and found a similar situation, but did not give a solution.

Later I tried to add constraints to get it. Specify the physical location of bufpll directly:

INST hdmi_encoder_0/hdmi_encoder_0/tx_bufpll_inst LOC= BUFPLL_X1Y5;

The estimated reason is that bufpll and OSERDES cannot be mapped because they are not in a bank. see picture 1.

Ref

1.S6 constraints for DDR A/D data, From Xilinx User community Forums

2. Introduction and use of Spartan-6 clock management module

European Socket Connector,30 Position European Socket Connector,Right Angle Male European Socket Connector,Male European Socket Connector

Dongguan Yangyue Metal Technology Co., Ltd , https://www.yyconnector.com